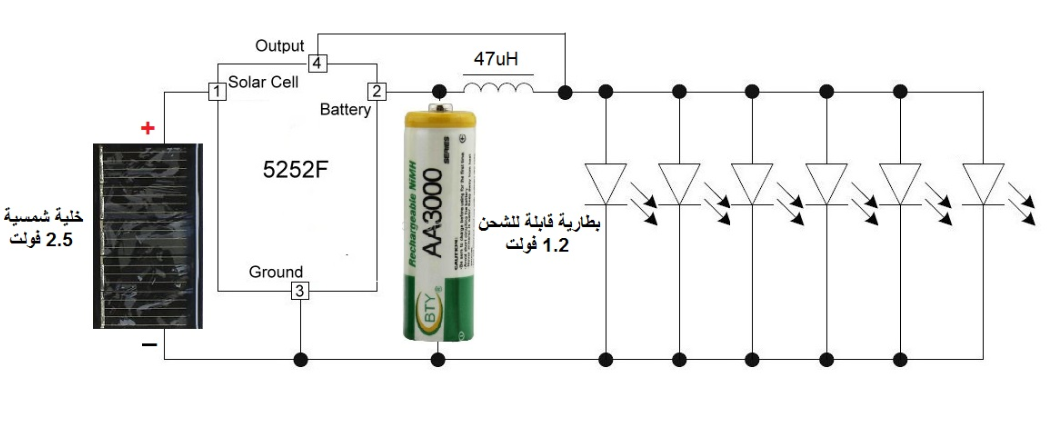

This pin is required in minimum systems, that want to use an 8286 or 8287 data bus transceiver.This Outdoor LED Solar Garden Lights project is a hobby circuit of an automatic garden light using a LDR and 6V/5W solar panel.

5252f chip diagram code#

QS1 QS0 Status 0 0 No operation 0 1 First byte of op code from queue 1 0 Empty the queue 1 1 Subsequent byte from queueĭT/R : Data Transmit/Receive. These signals indicate the status of the internal 8086 instruction queue according to the table shown below The signal must be active high(1) for at least four clock cycles. RESET : This pin requires the microprocessor to terminate its present activity immediately. Its an asymmetric square wave with a 33% duty cycle. The clock input provides the basic timing for processing operation and bus control activity. The input is internally synchronized during each of the clock cycle on leading edge of the clock.ĬLK : Clock Input. If the TEST pin goes low(0), execution will continue, else the processor remains in an idle state. TEST’ : This examined by a ‘WAIT’ instruction. The LOCK signal will be active until the completion of the next instruction. It indicates that other system bus masters have not been allowed to gain control of the system bus while LOCK’ is active low(0). RQ’/GT0′ have higher priority than RQ’/GT1′. These pins are used by local bus masters used to force the microprocessor to release the local bus at the end of the microprocessor’s current bus cycle. This pin signal indicates what mode the processor will operate in. It is active low(0) during T2, T3 and Tw of each interrupt acknowledge cycle. This input has been synchronized internally. A transition made from low(0) to high(1) initiates the interrupt at the end of the current instruction. NMI is non-maskable internally by software. A subroutine is then vectored through an interrupt vector lookup table which is located in the system memory. This is an edge triggered input which results in a type II interrupt. This signal is active high(1) and has been synchronized internally. This can be internally masked after resulting the interrupt enable flag.

If any interrupt request is found pending, the processor enters the interrupt acknowledge cycle. This is sampled during the last clock cycles of each instruction for determining the availability of the request.

5252f chip diagram generator#

The signal made available by the devices is synchronized by the 8284A clock generator to provide ready input to the microprocessor. READY : This is the acknowledgement from the memory or slow device that they have completed the data transfer. S7 signal is available during T2, T3 and T4. 8-bit device connected to upper half of the data bus use BHE (Active Low) signal. It is used to enable data onto the most significant half of data bus, D8-D15.

S2 S1 S0 Characteristics 0 0 0 Interrupt acknowledge 0 0 1 Read I/O port 0 1 0 Write I/O port 0 1 1 Halt 1 0 0 Code access 1 0 1 Read memory 1 1 0 Write memory 1 1 1 Passive stateĪ16/S3, A17/S4, A18/S5, A19/S6 : The specified address lines are multiplexed with corresponding status signals.Ī17/S4 A16/S3 Function 0 0 Extra segment access 0 1 Stack segment access 1 0 Code segment access 1 1 Data segment accessīHE’/S7 : Bus High Enable/Status. Any change in S2, S1, S0 during T4 indicates the beginning of a bus cycle. These are used by the 8288 bus controller for generating all the memory and I/O operation) access control signals. These pins are active during T4, T1 and T2 states and is returned to passive state (1,1,1 during T3 or Tw (when ready is inactive). These are multiplexed with status signals.

5252f chip diagram software#

Difference between Hardware and Software.Random Access Memory (RAM) and Read Only Memory (ROM).Program for Binary To Decimal Conversion.Program for Decimal to Binary Conversion.Addressing modes in 8086 microprocessor.Addressing modes in 8085 microprocessor.Priority Interrupts | (S/W Polling and Daisy Chaining).BUS Arbitration in Computer Organization.Bus organization of 8085 microprocessor.General purpose registers in 8086 microprocessor.Memory Segmentation in 8086 Microprocessor.

0 kommentar(er)

0 kommentar(er)